Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

lab experiment of electronics and communication engg.

Typology: Lab Reports

1 / 58

This page cannot be seen from the preview

Don't miss anything!

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

ANALOG ELECTRONICS LABORATORY LAB MANUAL – 15ECL III-SEMESTER 2016-

81/1, 182/1, Hoodi Village, Sonnenahalli, K.R. Puram, Bengaluru, Karnataka-560048.

CONTENTS

S.No Title Page No

Dept of ECE- GCEM Page iii

Course objectives:

This laboratory course enables students to get practical experience in design, assembly, testing and evaluation of

Rectifiers and Voltage Regulators.

BJT characteristics and Amplifiers.

JFET Characteristics and Amplifiers.

MOSFET Characteristics and Amplifiers.

Power Amplifiers.

RC-Phase shift, Hartley, Colpitts and Crystal Oscillators

Course outcomes:

Through this course, the students:

Acquire a basic knowledge in solid state electronics including diodes, MOSFET, BJT, and operational amplifier.

Develop the ability to analyze and design analog electronic circuits using discrete components.

Observe the amplitude and frequency responses of common amplification circuits.

Design, construct, and take measurement of various analog circuits to compare experimental results in the laboratory with theoretical analysis.

Dept of ECE- GCEM Page iv

LAB INSTRUCTIONS

Do’s Ensure your presence five minutes before the commencement of the lab.

Attend all the lab sessions without fail.

Come well prepared for every lab session.

Complete and Bring the Lab records regularly.

Ensure the proper polarity of cables before connecting the kits.

Ensure the checking of the circuit of circuit connections before turning ON the circuit.

Tuck in your shirts and not to play with instruments laid on the bench.

Wearing loose garments inside the lab is strictly prohibited.

You have to wear shoes compulsorily.

Keep the space around you clear for others.

Don’ts Don‟t bring the Cell phone and food items to Lab.

Don‟t switch ON voltage supplies after making circuit connections in the absence of the teacher.

Don‟t rotate the Knobs unnecessarily.

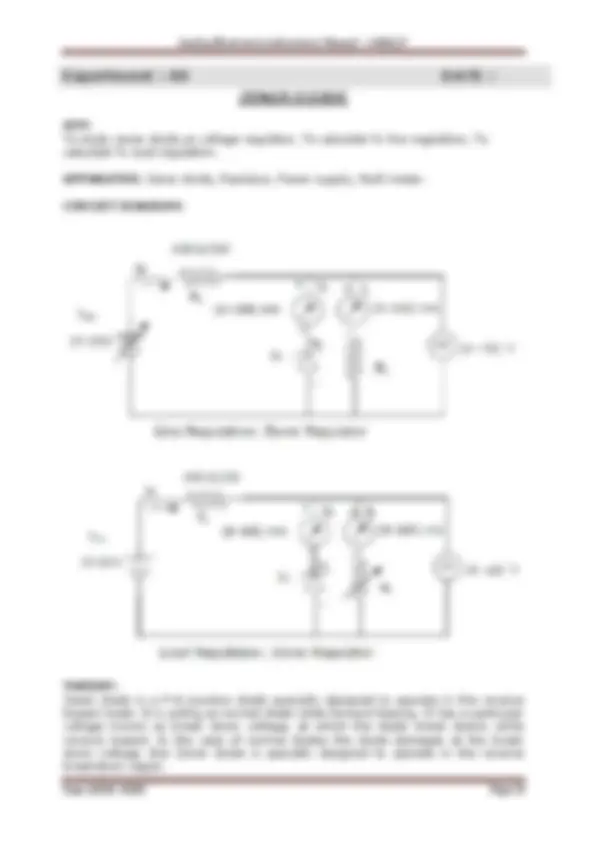

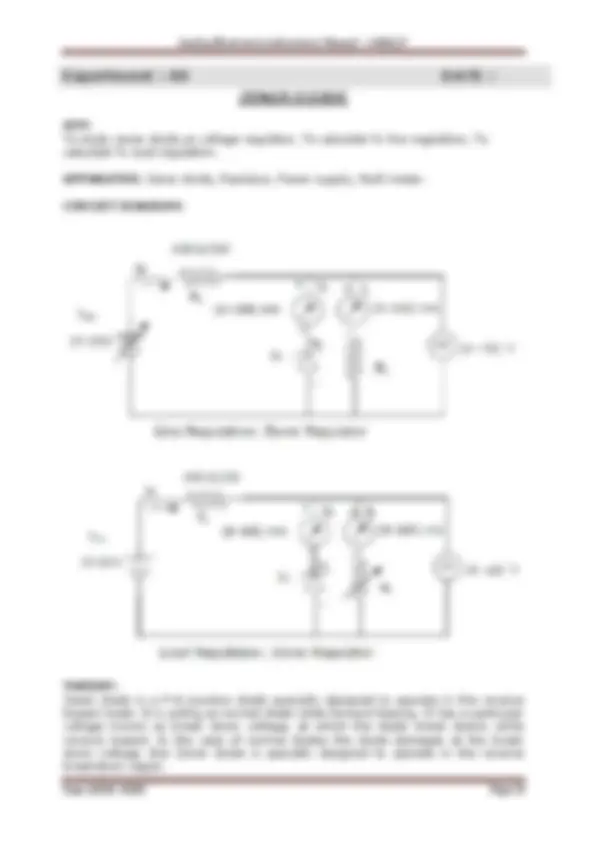

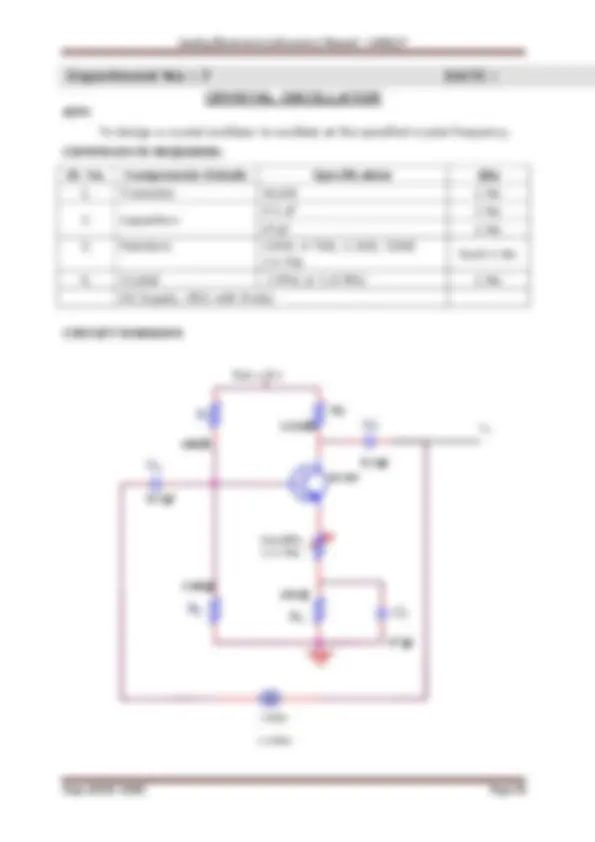

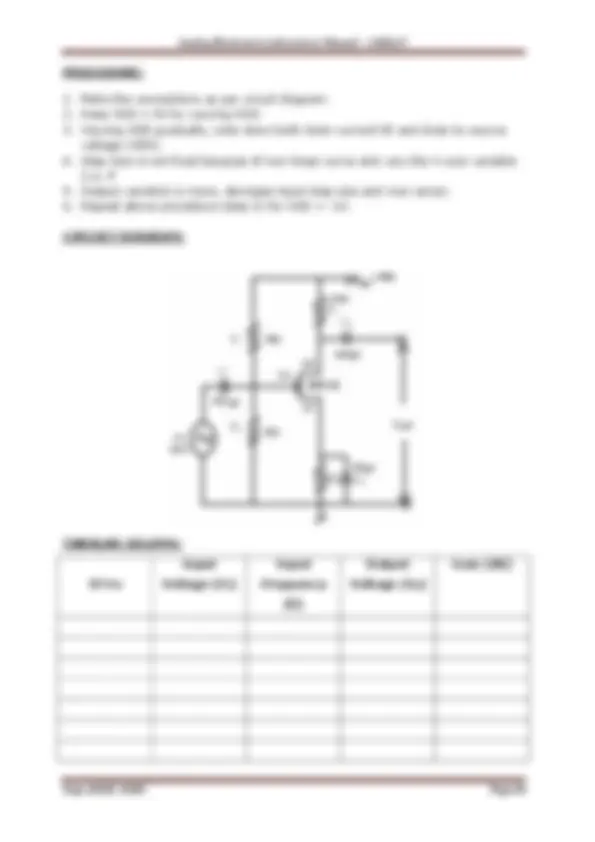

Experiment No : 1 DATE : FULL WAVE RECTIFIER

AIM: To study the full wave rectifier and to calculate ripple factor and efficiency and Regulation with filter and without filter.

COMPONENTS REQUIRED:

Sl. No. Components Details Specification Qty

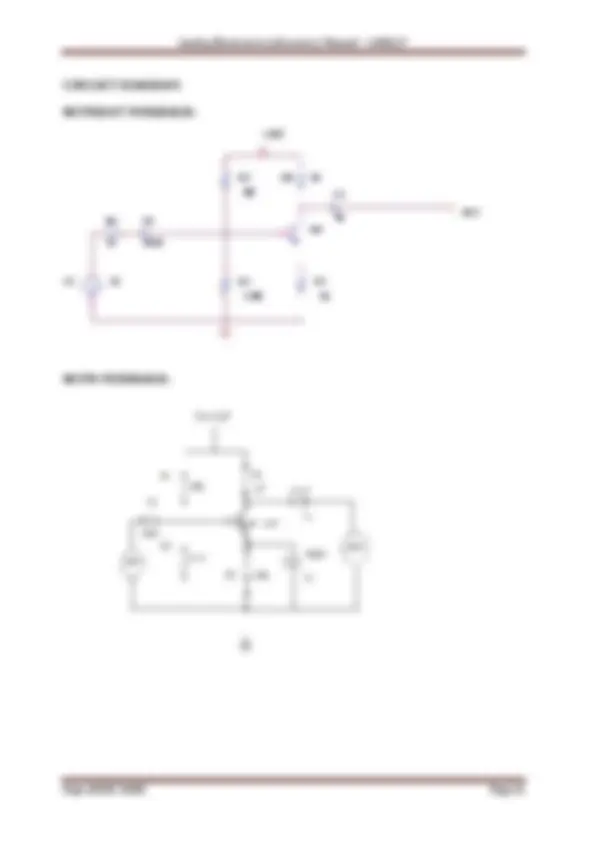

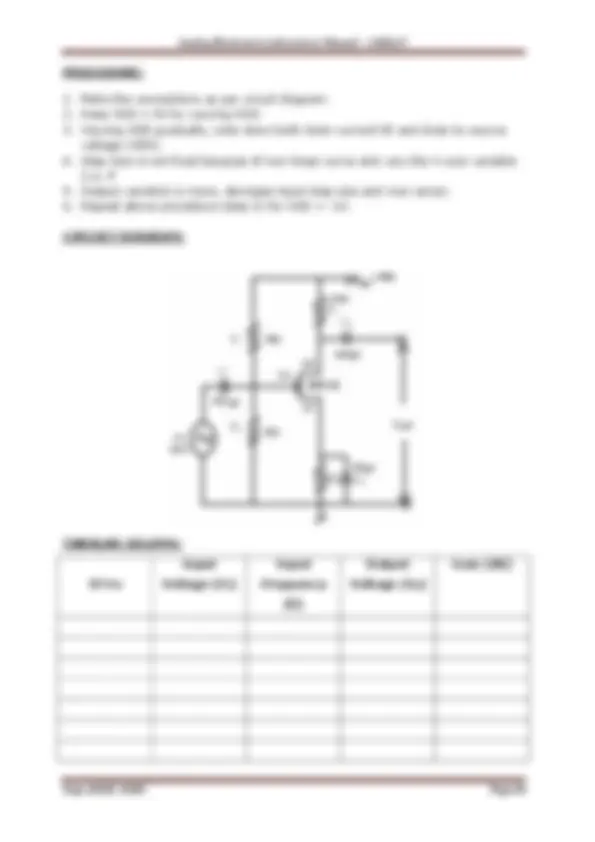

THEORY: The center tapped full wave rectifier circuit is similar to a half wave rectifier circuit, using two diodes and a center tapped transformer. Both the input half cycles are converted into unidirectional pulsating DC. CIRCUIT DIAGRAM: FULL WAVE RECTIFIER WITHOUT FILTER CAPACITOR Step down C BY127^ 0.1UF

A K

RL

AC (230V/50HZ)

12V

12V

0

Transformer A

Ammeter(0-250mA)

VO(DC)

BY

A K

Vin rms = 12V Vin m = 2Vin rms = 16.97V VO DC = 2Vm/ = 10.8V Given VO DC = 10V IO DC = 100mA RL = VO DC / IO DC = 100

Ripple = r = Vo rms / VO DC = 0. Design for the filter capacitor Ripple = 1/(43 f C RL)

Given r =. C = 1/(43 f r RL) RL = 100 f = 50Hz

= 470UF

FL

NL FL

(230V/50HZ)

C BY127^ 0.1UF

A K

RL

AC

12V

12V

0

Step down Transformer

A

Ammeter(0-250mA)

470UF

C

BY

A K

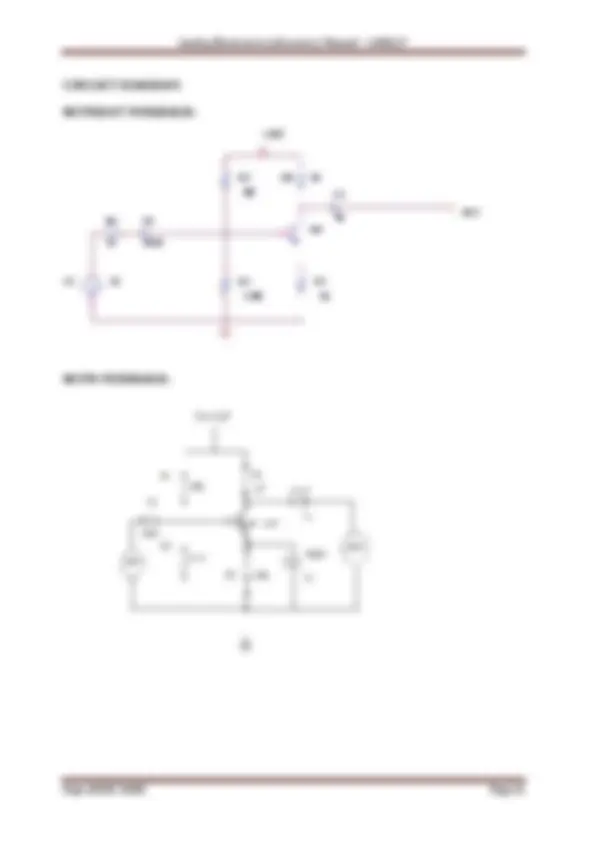

Experiment No : 1b DATE : BRIDGE RECTIFIER

AIM: To study the bridge rectifier and to calculate ripple factor and efficiency and regulation with filter and without filter. COMPONENTS REQUIRED:

Sl. No. Components Details Specification Qty

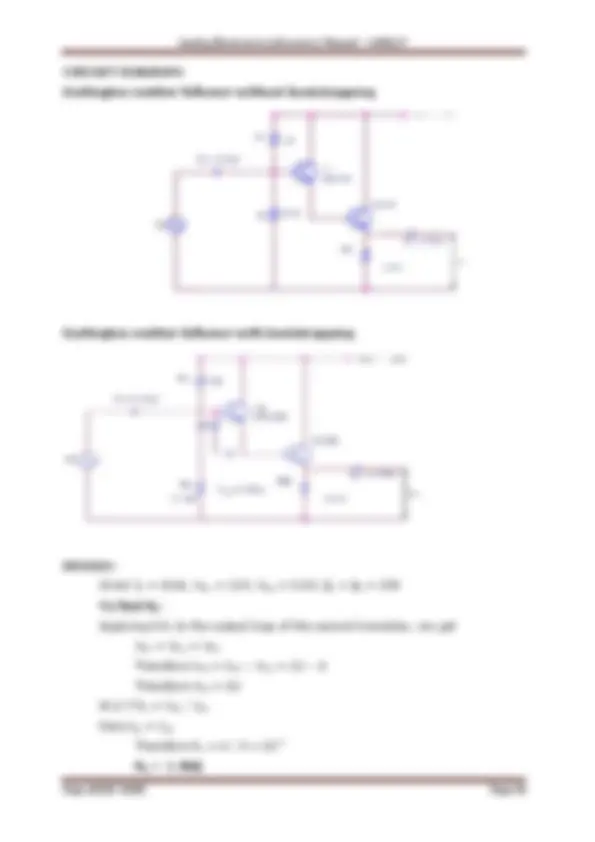

THEORY: The bridge rectifier circuit is essentially a full wave rectifier circuit, using four diodes, forming the four arms of an electrical bridge. To one diagonal of the bridge, the ac voltage is applied through a transformer and the rectified dc voltage is taken from the other diagonal of the bridge. The main advantage of this circuit is that it does not require a center tap on the secondary winding of the transformer; ac voltage can be directly applied to the bridge. The bridge rectifier circuit is mainly used as a power rectifier circuit for converting ac power to dc power, and a rectifying system in rectifier type ac meters, such as ac voltmeter in which the ac voltage under measurement is first converted into dc and measured with conventional meter. CIRCUIT DIAGRAM: BRIDGE RECTIFIER WITHOUT FILTER CAPACITOR

RL

BRIDGE 1

4

3

2

C 0.1UF AC (230V/50HZ)

12V

12V

0

Step down Transformer

Vo

A

Ammeter(0-250mA)

Vin rms = 12V Vin m = 2Vin rms = 16.97V VO DC = 2Vm/ = 10.8V Given VO DC = 10V IO DC = 100mA RL = VO DC / IO DC = 100

Ripple = r = Vo rms / VO DC = 0. Design for the filter capacitor Ripple = 1/(43 f C RL)

Given r =. C = 1/(43 f r RL) RL = 100 f = 50Hz

= 470UF

Efficiency = PDC /PAC = (I^2 DC * RL) / [(Irms)^2 * (RL + RF)]

FL

NL FL

C 47 0UF

RL

B RIDGE 1 4

3

2

C 0.1UF A C(230 V/50 HZ)

12V

12V

0

Step down Transformer

Vo

A

Ammeter(0-250mA)

Design a clamping circuit for the given output. COMPONENTS REQUIRED:

Sl. No. Components Details Specification Qty

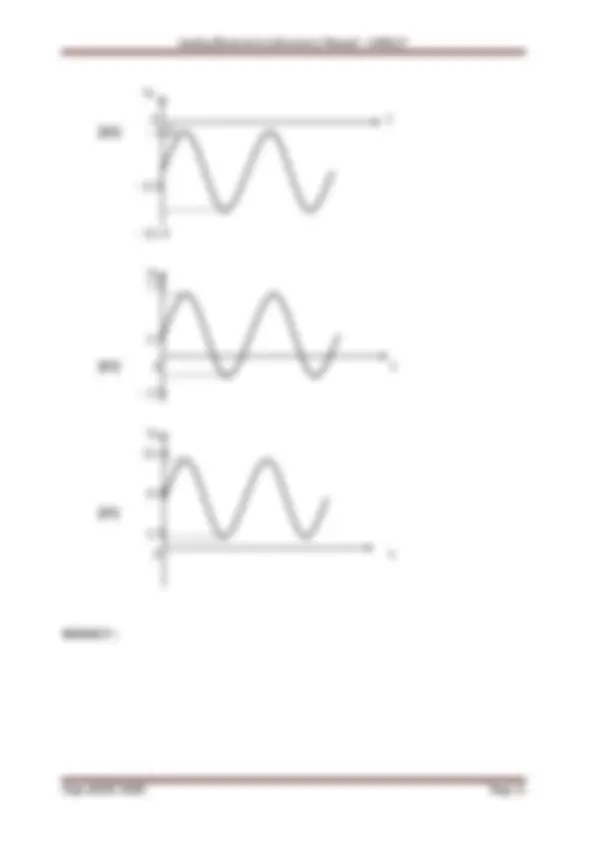

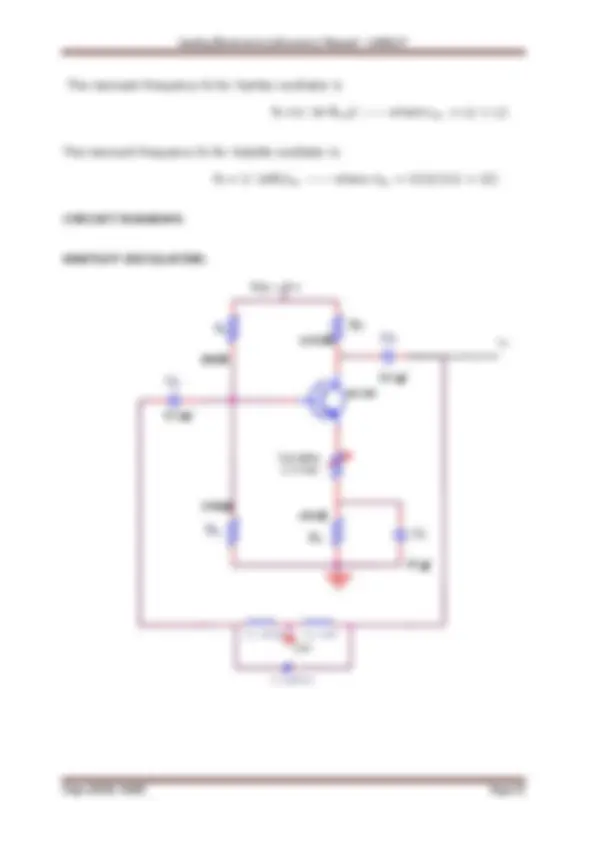

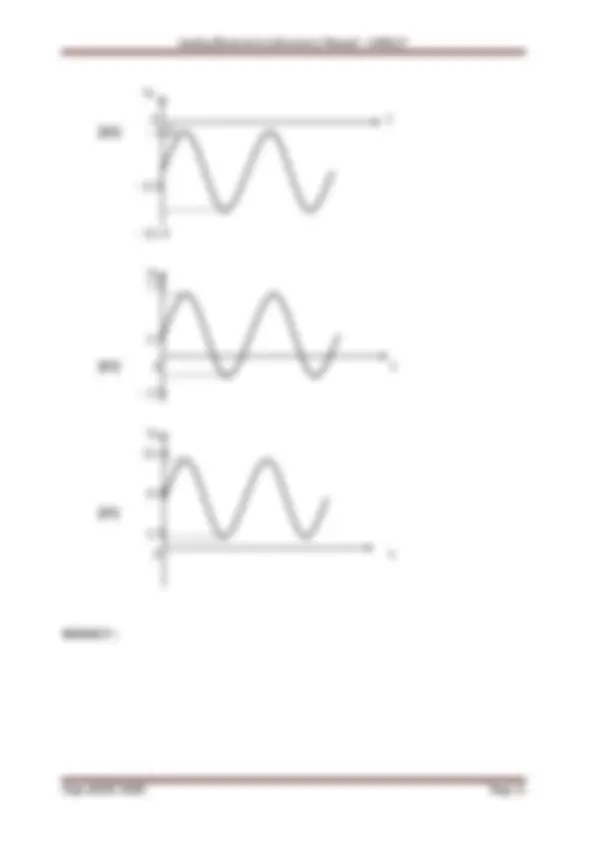

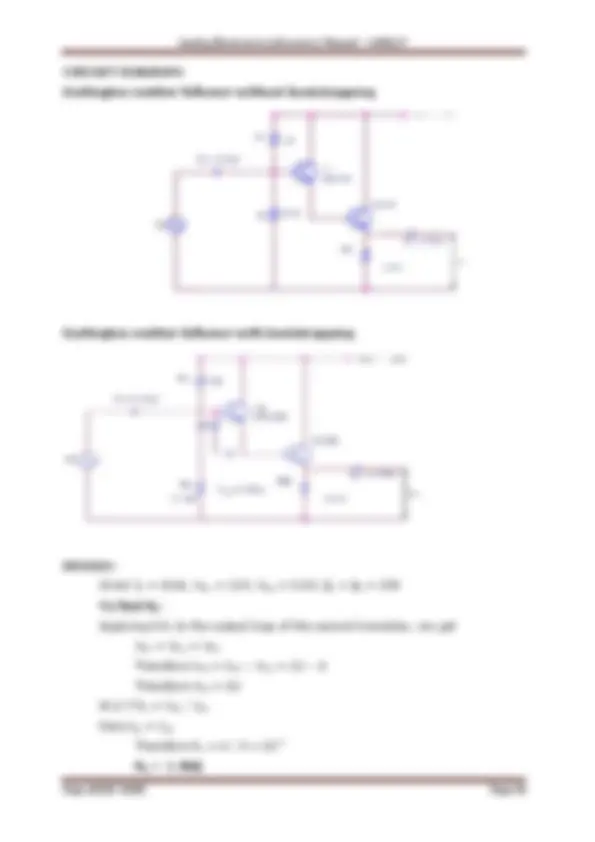

THEORY: A clamper is one, which provides a D.C shift to the input signal. The D.C shift can be positive or negative. The clamper with positive D.C shift is called positive clamper and clamper with negative shift is called negative clamper. Consider a clamper circuit shown below.

In the positive half cycle as the diode is forward biased the capacitor charges to

Then in the positive half cycle diode is forward biased and applying KVL to the loop, Vin – VC – V 0 = 0 V 0 =Vin – VC When Vin = 0 V 0 = 0 - 4.5 = - 4.5V Vin = 5V V 0 = 5 – 4.5 = 0.5V In the negative half cycle When Vin = - 5V V 0 = - 5 – 4.5 = - 9.5V The output shifts between 0.5V and – 9.5V.Here the output has shifted down by 4.5V

D BY 127

0.1u

Vin Vo

C

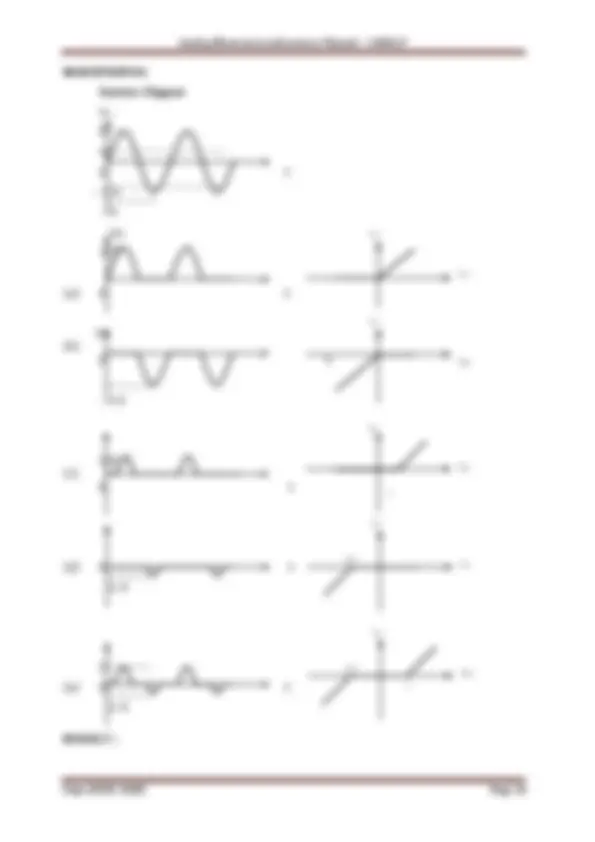

The peak to peak voltage at the output of a clamper is the same as that of the input. CIRCUIT DIAGRAM AND DESIGN: Given Vin = 10V (p-p) A] In the positive half cycle: Diode is forward biased. Applying KVL to loop 1 Vin – VC – VD = 0 VC = Vin – VD = 5 - 0.5 4.5V In the negative half cycle: Vin – VC – V 0 = 0 V 0 = Vin – VC When Vin = 0 V 0 = - 4.5V When Vin = 5V V 0 = 0.5V When Vin = - 5V V 0 = - 9.5V B]In the negative half cycle: Diode is forward biased Applying KVL to loop 1 Vin + VC + VD = 0 VC = - ( Vin + VD) VC = - (-5 + 0.5) = 4.5V In the positive half cycle: Diode is reverse biased. Apply KVL to the loop Vin + VC – V 0 = 0 V 0 = Vin + VC When Vin = 0 V 0 = 4.5V When Vin = 5V V 0 = 5 + 4.5 = 9.5V When Vin = - 5V V 0 = - 0.5V

D BY 127

0.1u

Vin Vo

C

BY127 D

0.1u

Vin Vo

C

E]In the negative half cycle: Assume VR = 2V Diode is forward biased and capacitor charges. Apply KVL to the loop Vin + VC + VD + VR = 0 VC = - ( Vin + VR + VD) = - (- 5 + 0.5 + 2) = 2.5V From the fig. we see that Vin + VC – V 0 = 0 V 0 = Vin + VC When Vin = 0 V 0 = 2.5V When Vin = 5V V 0 = 7.5V When Vin = - 5V V0 = - 2.5V F] VR = 2V In the negative half cycle: Diode is forward biased and capacitor charges. Apply KVL to loop 1 Vin + VC + VD - VR = VC = - ( Vin + VD - VR) = - (- 5 + 0.5 – 2) = 6.5V From the circuit we see that, Vin + VC - V 0 = V 0 = Vin – VC When Vin =0V V 0 =6.5V When Vin = 5V V 0 = 11.5V When Vin = - 5V V 0 = 1.5V PROCEDURE:

Vo

0.1u

BY127 D

VR

C Vin

Vo

0.1u

Vin^ C BY127^ D

-^ +

VR

Vin 5V

0 t

V 0

0 t [A]

[B] 0 t

[C] t

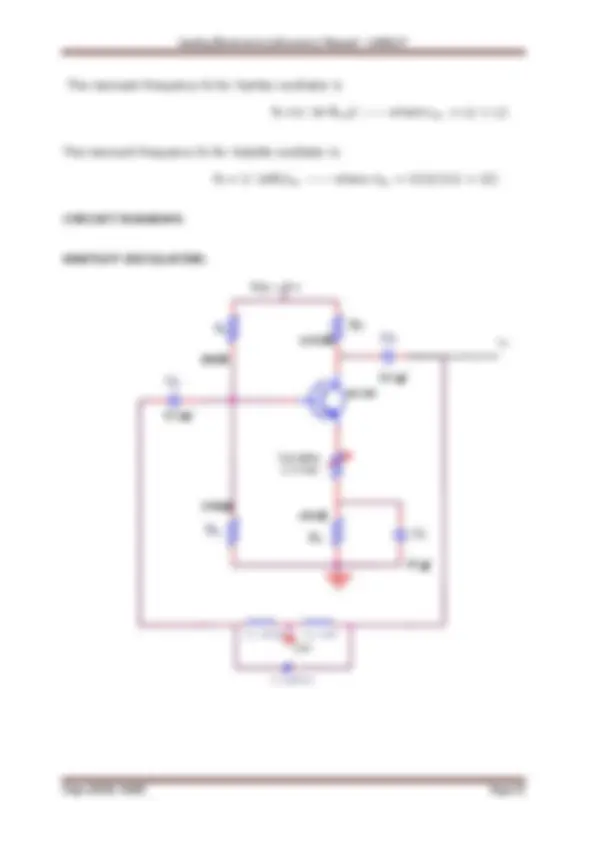

Experiment No : 2b DATE : CLIPPING CIRCUITS

AIM: Design a clipping circuit for the given values. COMPONENTS REQUIRED:

Sl. No. Components Details Specification Qty

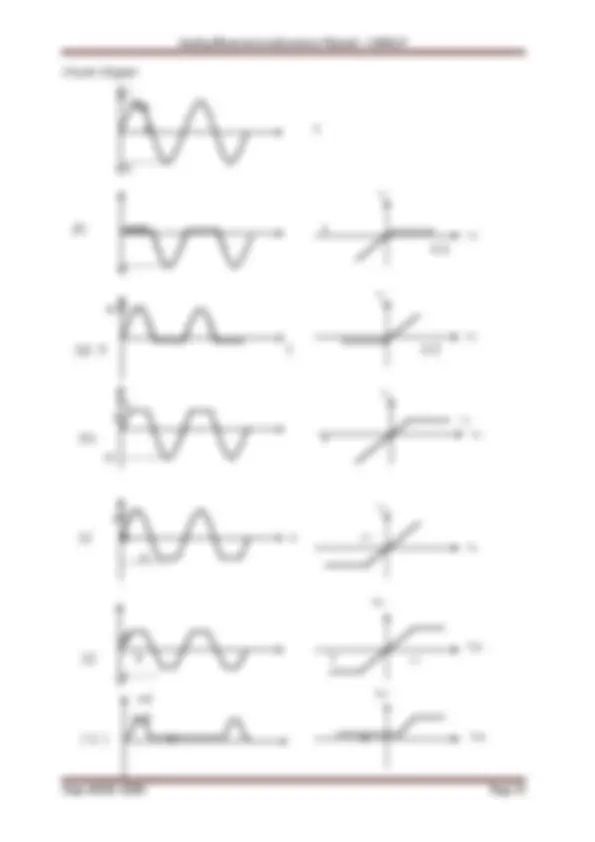

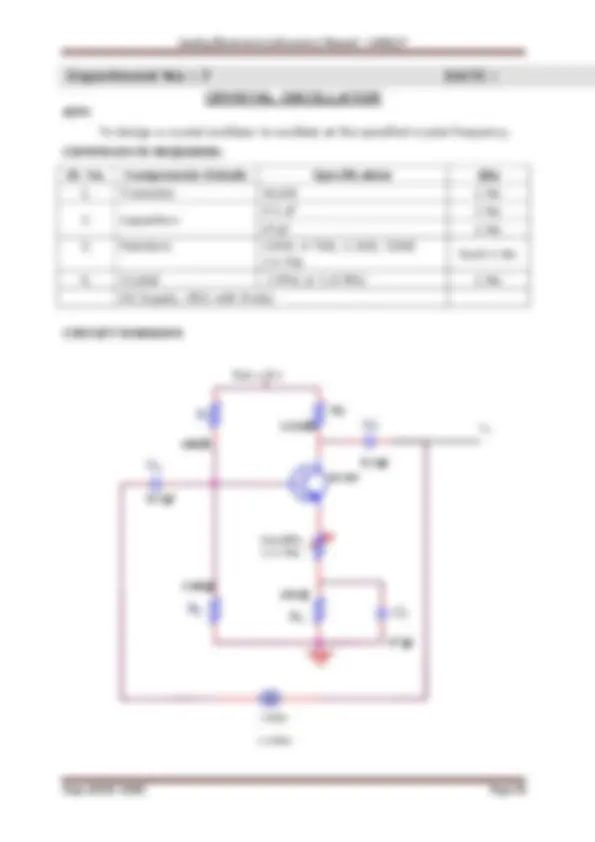

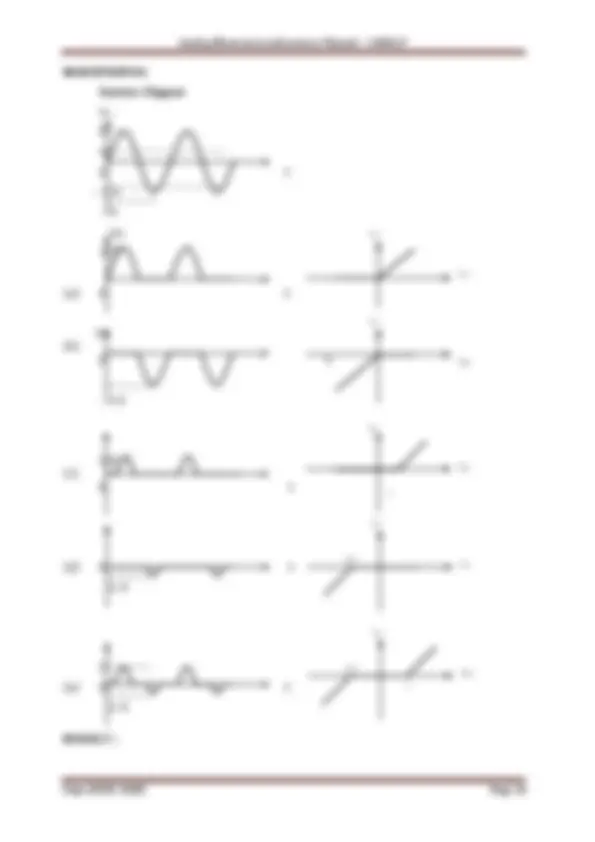

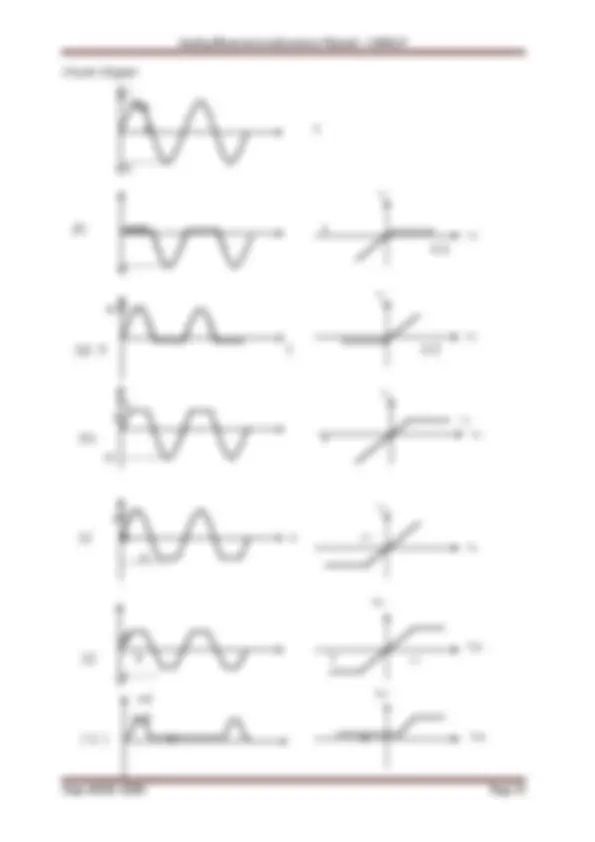

THEORY: The process by which the shape of a signal is changed by passing the signal through a network consisting of linear elements is called linear wave shaping. Most commonly used wave shaping circuit is clipper. Clipping circuits are those, which cut off the unwanted portion of the waveform or signal without distorting the remaining part of the signal. There are two types of clippers namely parallel and series. A series clipper is one in which the diode is connected in series with the load and a parallel clipper is one in which the diode is connected in parallel with the load.

CIRCUIT DIAGRAM AND DESIGN: Assume Vin = 10V (Peak to Peak) (a) Consider the circuit in fig. 1 In the positive half cycle D is forward biased V 0 = Vin – 0.5 = 5 – 0.5 = 4.5 (0.5V is the diode drop) In the negative half cycle D is reverse biased V 0 = 0V (b) Consider the circuit in fig. 2 In the positive half cycle D is reverse biased V 0 = 0V In the negative half cycle D is forward biased Applying KVL to the loop Vin + VD – V 0 = 0 V 0 = Vin + VD = -5 + 0.5 = - 4.5V

10k

D Vin BY Vo

(a)

10k

D

Vin BY127 Vo

(c) Consider the circuit in fig. 3 Given VR = 2.5V In the positive half cycle (i) When |Vin| > |VD + VR|, D is forward biased Applying KVL, we get Vin = VD + VR + V 0 V 0 = Vin – VD – VR V 0 = 5 – 0.5 – 2. V 0 = 2V (ii) When |Vin| < |VD + VR|, D is reverse biased V 0 = 0V In the negative half cycle , D is reverse biased V 0 = 0V (d) Consider the circuit in fig. 4 Assume VR = 3V In the positive half cycle , D is reverse biased V0 = 0V In the negative half cycle (i) When |Vin| > |VD + VR|, D is forward biased Applying KVL, we get Vin = - VD - VR + V 0 V 0 = Vin + VD + VR V 0 = -5 + 0.5 + 3 V 0 = -1.5V (ii) When |Vin < |VD + VR|, D is reverse biased V 0 = 0V

D BY 10k

VR

Vin (^) Vo

VR

10k

D BY Vin Vo