Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

It contains details about jfets and how they may be used

Typology: Essays (university)

1 / 28

This page cannot be seen from the preview

Don't miss anything!

Like bipolar junction transistor, junction field effect transistor JFET is also a three-terminal device but it is a unipolar device, which shall mean that the current is made of either electron or hole carrier.

The operation of JFET is controlled by electric field effect. Thus, JFET is a voltage-controlled current source device, whereas BJT is a current-controlled source device.

There are two types of JFET namely n -channel and p -channel. n -channel type means the carrier type in the conducting channel is electron. Likewise, for p -channel type, the carrier type in conducting channel is hole.

JFET has three terminals, which are gate G, drain D and source S. The gate is used to control the flow of carrier from source to drain. Source is the terminal that emits carrier and the drain is the terminal that receives carrier.

The structures of n -channel and p -channel JFET are shown in Fig. 4.1.

(a) n -channel JFET (b) p -channel JFET Figure 4.1: The structures of n -channel and p -channel

The symbols of n -channel and p -channel JFETs are shown in Fig. 4.2.

(a) n -channel JFET (b) p -channel JFET Figure 4.2: Symbols of n -channel and p -channel JFET

In normal operation, the gate of JFET is always reverse-biased. Thus, an n - channel type, the gate is biased with negative voltage i.e. gate voltage is less than zero volt VG < 0, whilst for p -channel type, the gate is biased with positive voltage i.e. gate voltage is greater than zero voltage VG > 0.

The source and drain are biased according to the channel type or carrier type. If it is an n -channel JFET (electron as carrier), the source is biased with negative voltage while the drain is biased with positive voltage. Alternatively, it can be biased such that the drain voltage VD is greater than the source voltage VS. i.e. VD > VS.

If it is a p -channel JFET (hole as carrier), the source is biased with positive voltage while the drain is biased with negative voltage. Alternatively, it can be biased such that the drain voltage VD is less than the source voltage VS. i.e. VD < VS.

Figure 4.3 shows the bias condition for an n -channel JFET.

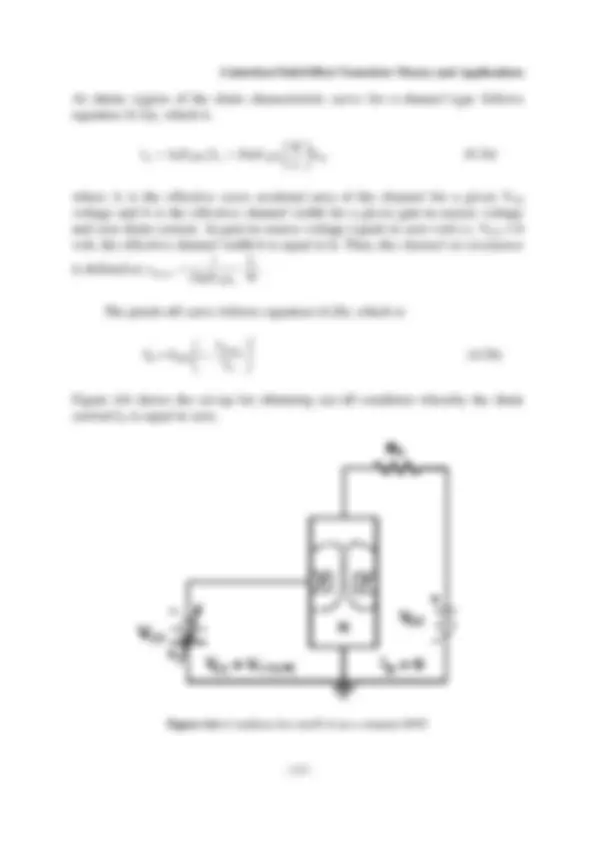

Between point A and B, it is the ohmic region of the JFET. It is the region where the voltage and current relationship follows ohm's law. At point B, the drain current is at maximum for VGS = 0 condition and is defined as IDSS. It is the pinch-off point, where there is no increase of current as drain-to-source voltage VDS is further increased. The VDS voltage at this point is called pinch-off voltage VP. It is also the voltage point where drain-to-gate voltage VDG produces enough depletion thickness to narrow the channel so that the resistance of the channel will increase significantly. Since VGS = 0, VDS is also equal to VDG. Thus, in general the pinch-off voltage Vp is

Vp = VDS(P) - VGS (4.1)

where VDS(P) is the pinch-off drain-to-source voltage for a VGS value. IDSS and VP are constant values listed by the manufacturer for a given JFET type, which are the drain current and pinch-off voltage at gate-to-source voltage VGS = 0.

At point C, the JFET begins to breakdown where the ID increases rapidly and it is an irreversible breakdown.

Different value of VGS produces different drain characteristic curve. For n - channel JFET, as VGS decreases, ID current and VDS(P) decreases. There is a VGS value that no drain current ID is registered irrespective of the drain-source voltage VDS. This gate-to-source voltage VGS is the cutoff gate-to-source voltage VGS(off). Since there is no ID current, VDS must be zero. Thus, from equation (4.1) VGS = -VP. Equation (4.1) can also now be written as VDS(P) = VGS – VGS(off).

Figure 4.5: Drain characteristics of n -channel JFET of different VGS

At ohmic region of the drain characteristic curve for n -channel type follows equation (4.2a), which is

D D n X D n L V DS I AqN E 2 bqN W

= μ = μ (4.2a)

where A is the effective cross sectional area of the channel for a given VGS voltage and b is the effective channel width for a given gate-to-source voltage and zero drain current. At gate-to-source voltage equals to zero volt i.e. VGS = 0 volt, the effective channel width b is equal to h. Thus, the channel on-resistance

is defined as r hqN

L DS on( ) (^) D n W = ⋅

1 2 μ

The pinch-off curve follows equation (4.2b), which is

2

P

DS(P) V

V (^1)

− (4.2b)

Figure 4.6 shows the set-up for obtaining cut-off condition whereby the drain current ID is equal to zero.

Figure 4.6: Condition for cutoff of an n -channel JFET

Figure 4.7: Transfer characteristics curve of an n -channel JFET

The curve is a parabolic curve, which can be expressed mathematically as

I I

V D DSS V

GS GS off

= −

1

2

( )

The forward transconductance gm of the JFET is defined as the change of drain current for a given change in gate-source voltage VGS and it is expressed as

g

I m V

D GS

=

∆ ∆

From the transfer characteristic curve, one will realize that the transconductance of the device is at maximum when VGS is at zero voltage. The value of gm at VGS = 0 is always given in the manufacturer data sheet of the device, which is denoted as gm0. If gm0 is given, gm for a given VGS can be calculated from equation (4.5).

g g V m m V GS GS off

= −

0 1 ( )

Equation (4.5) can be derived from equation (4.4) by differentiating drain current with respect to gate-to-source voltage i.e. dID/dVGS.

g

dI dV

I V

V m V

D GS

DSS GS Off

GS GS off

= = − −

2 1 ( ) ( )

Comparing equation (4.5) and (4.6), gm0 shall be

g

I m V

DSS GS off 0

2 = − ( )

Thus, given the values of IDSS and VGS(off), the transconductance of the device at VGS = 0 can be determined.

From equation (4.3) and (4.5), transconductance gm can be expressed as

g (^) m = g (^) m 0 I (^) D / IDSS (4.8)

Thus, the transconductance gm of JFET for a given drain current ID value, can be obtained.

Since the gate of JFET is reverse-biased, the input impedance is very high. This is one advantage of JFET over bipolar junction transistor. In JFET data sheet, the input impedance is given by gate reverse current IGSS for a given gate-source voltage VGS. Thus, input impedance can be expressed as

R

V IN gate I

GS GSS

The purpose of biasing the device is to select the right dc gate-to-source voltage for the JFET in order to establish a desired value of drain current. Listed here are some standard methods.

As mentioned earlier, the purpose of biasing is to select the right dc gate-source voltage for the JFET to establish a desired value of drain current. Once it is established. The source resistance RS can be calculated using equation (4.12).

V I

GS D

Example 4. Determine the value of RS required to self-bias an n -channel JFET with IDSS = 25mA, VGS(off) = -10V, VGS = -5V and its transconductance gm.

Solution Drain current ID at gate-to-source VGS = -5V is

2 −

V V

GS GS off( )

= 25mA 1

5 10 6 25

2 −

− −

^

^

=

V V

. mA

The source resistance RS is

V I

V mA

GS D

= =

5 6 25 800 . Ω

Transconductance gm at VGS = 0, g

I m V

DSS GS off 0

2 = − ( )

2 25 10 5

x mA V mA /V

Thus, the transconductance gm at ID = 6.25mA is,

g (^) m = g (^) m 0 I (^) D / IDSS= 5 mA / V 6 25.^ mA^25 mA =2 5. mA /V

The purpose of midpoint bias is to allow maximum drain current ID swing. From the drain transfer characteristic curve, the midpoint bias occurred at drain current ID corresponds to IDSS/2 and at approximately gate-to-source voltage VGS equals to VGS(off)/4. Indeed when drain current equals to ID = IDSS/2, gate-to- source voltage is VGS = 0.29 time of gate-to-source cutoff voltage VGS(off). The illustration is shown in Fig. 4.9.

Figure 4.9: The transfer characteristic curve showing midpoint-bias values for JFET

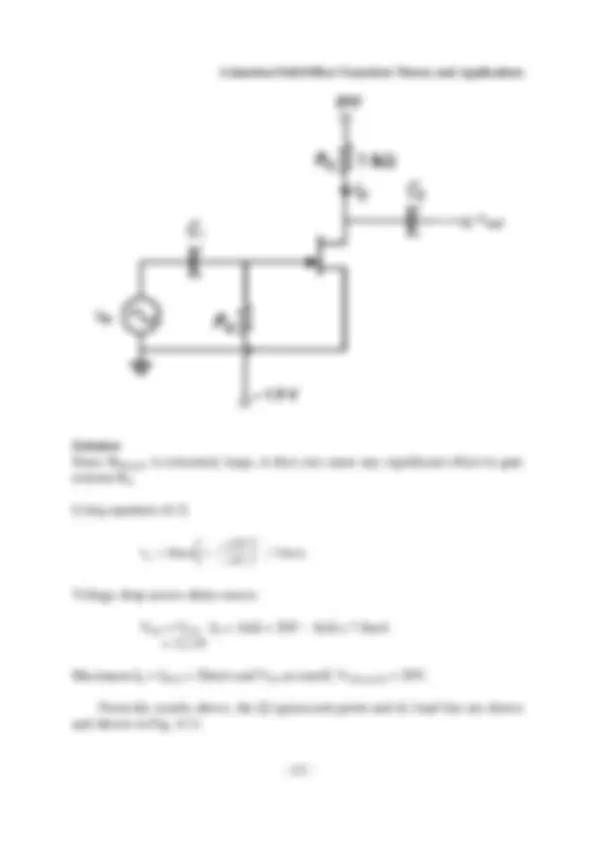

An n -channel JFET with voltage-divider bias is shown in Fig. 4.10. The voltage at the source of the JFET must be more positive than the voltage at the gate in order to keep the gate-source junction reverse-biased.

The source voltage VS is

The gate voltage VG is set by resistors R 1 and R 2 and is expressed by the following equation using voltage-divider concept.

V R R R G =^ VDD

(^2) 1 2

The gate-to-source voltage VGS is VGS = VG - VS

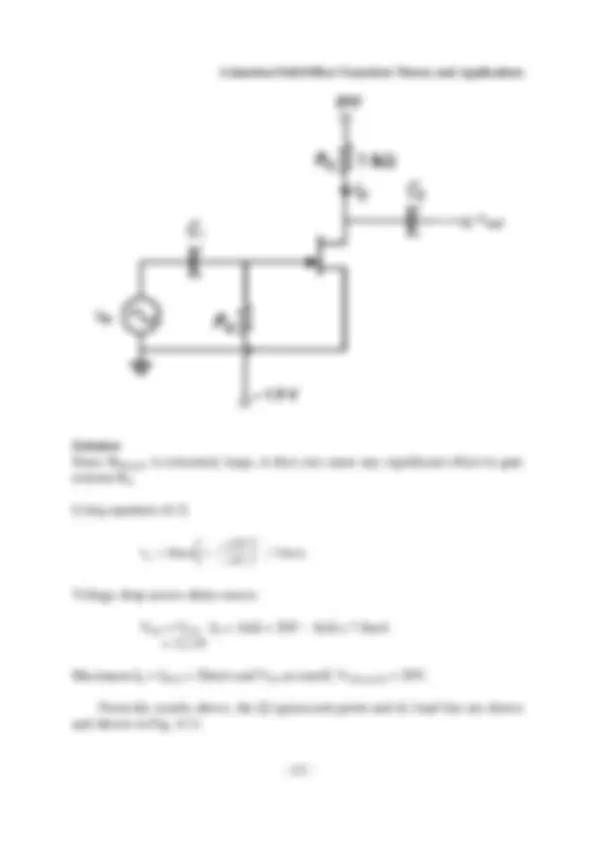

Solution Since RIN(gate) is extremely large, it does not cause any significant effect to gate resistor RG.

Using equation (4.3)

I mA

V V D =^ − mA

− −

^

(^20 1) =

15 4 7 8

. 2 .

Voltage drop across drain-source

VDS = VDD - ID x 1kΩ = 20V - 1kΩ x 7.8mA = 12.2V

Maximum ID = IDSS = 20mA and VDS at cutoff, VDS(cutoff) = 20V.

From the results above, the Q (quiescent)-point and dc load line are drawn and shown in Fig. 4.11.

Figure 4.11: The graph shows the dc load line and Q-point of the amplifier shown in Fig.

Example 4. Determine the approximate Q-point for the JFET biased with a voltage divider circuit as shown in the figure, given that the particular device has transfer characteristic curve as shown.

Solution From equation (4.13), for drain current ID = 0A, the gate-to-source voltage VGS is

R R R

(^2) VDD 1 + 2

2 2 2 2 2 2 8

.

..

M M M V

Ω Ω + Ω

^

^ = 4.0V

From Equation (4.15), for VGS = 0V, the drain current is

S

G R

V (^) = 4V/3.3kΩ = 1.2mA

= 8V - 1.8mA(680Ω + 3.3kΩ) = 0.83V

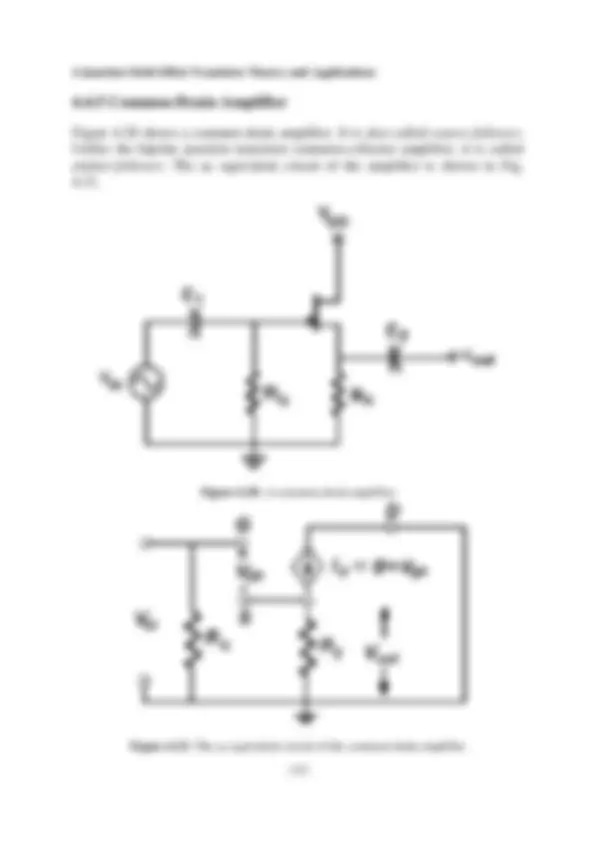

In this Section, the JFET is configured such that it works as a small-signal amplifier. Various methods of biasing configuration such common-drain, common-gate, and common-source configurations will be studied including its merit and demerit points.

The amplification can be achieved from n -channel JFET transfer characteristic and drain curves as they are shown in Fig. 4.12 and Fig. 4. respectively. Similarly, amplification can be achieved for p -channel JFET device.

As shown in Fig. 4.12, a small change of gate-to-source voltage VGS can result a large change of drain current ID.

Figure 4.12: Transfer characteristic curve of n -channel JFET showing signal amplification

Similarly, once can see that the above-mentioned change would also show in the change of drain-to-source voltage VDS as shown in Fig. 4.13.

Like in the case of bipolar junction transistor, the Q-point of the amplifier should be designed to set at the linear region of the transfer characteristic curve to avoid non-linearity distortion.

Figure 4.13: Drain curve of n -channel JFET showing signal amplification

Equation (4.4) defines dc transconductance as GS

m D V

g I ∆

= ∆. Thus, ac

transconductance is defined as gs

m d V

g = I. By rearranging the equation, ac drain

current is Id = gmVgs.

The hybrid π-model equivalent circuits of JFET are shown in Fig. 4.14. These circuits are applicable for JFET and MOSFET. The drain current Id is equal to gmVgs gate-source resistance rgs and output impedance = ro are introduced as shown in Fig. 4.14(a). If gate-to-source resistance rgs is assumed to be infinitely large and rO is large enough to be neglected, then the simplified equivalent circuit shall be Fig. 4.14(b). Output impedance ro of the JFET can be determined

The voltage gain AV of the JFET with an external ac source as input is defined as AV = Vout/Vin. For a self bias JFET amplifier, its ac equivalent circuit is shown in Fig. 4.16.

Figure 4.16: ac equivalent circuit

From the circuit, the output voltage Vout is Vout = -Vds = -IdRD and the input voltage Vin is Vin = Vgs = Id/gm. Thus, the voltage gain is equal to AV = Vout/Vin is

A

I R I g V d^ D g^ R d m

= − (^) / = − m D (4.18)

If output impedance ro of JFET is taken into consideration, the voltage gain AV will be reduced to

A g

R r V mR r

D O D O

= −

If there is a source resistance RS, where the ac equivalent circuit is shown in Fig. 4.17, voltage gain AV is reduced further because input voltage Vin is not just equal to gate-to-source voltage Vgs. The input voltage Vin is Vin =Vgs + VgsgmRS

= Vgs(1 + gmRS). Since output voltage Vout is Vout = -gmVgs

R r R r

D O D +^ O

. Therefore,

the ac voltage gain AV is

g g R

R r R r

m m S

D O ( 1 + ) D + O

Figure 4.17: ac equivalent circuit with external source resistance Rs

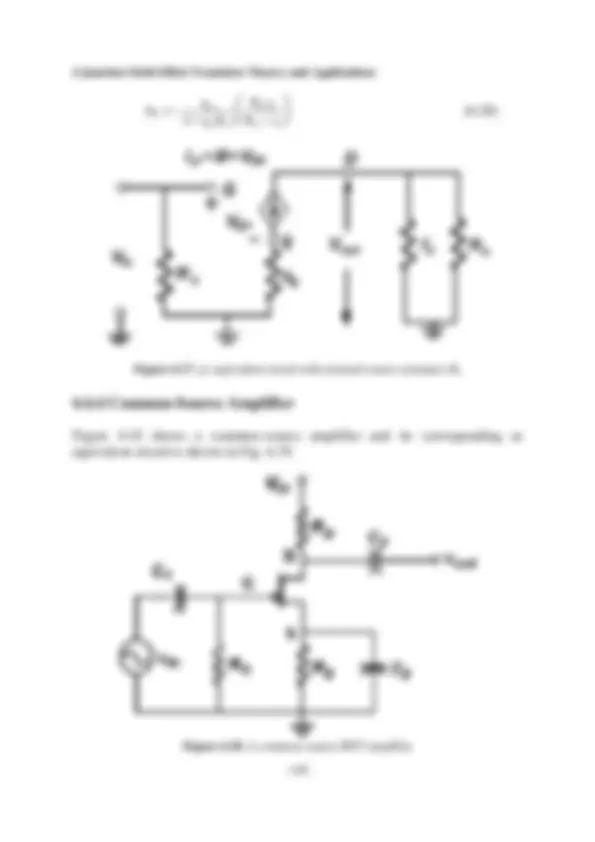

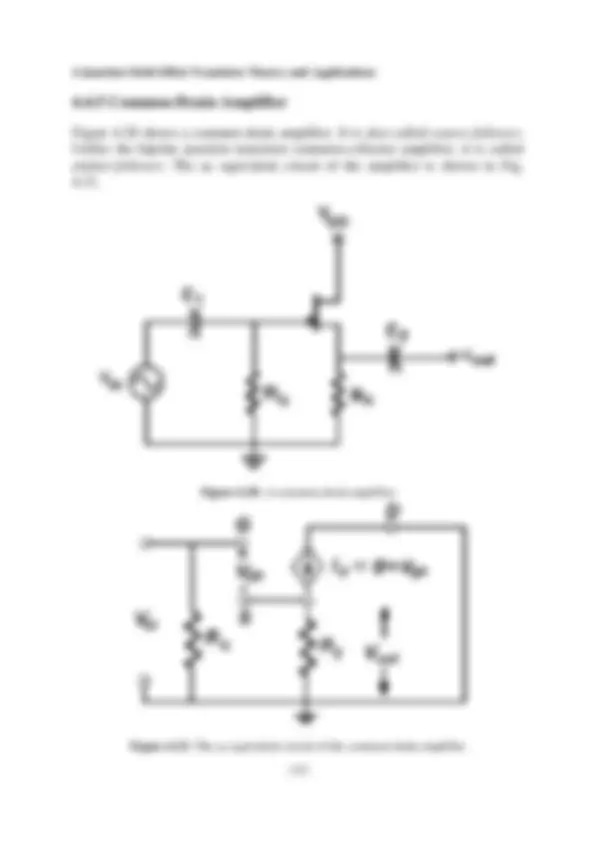

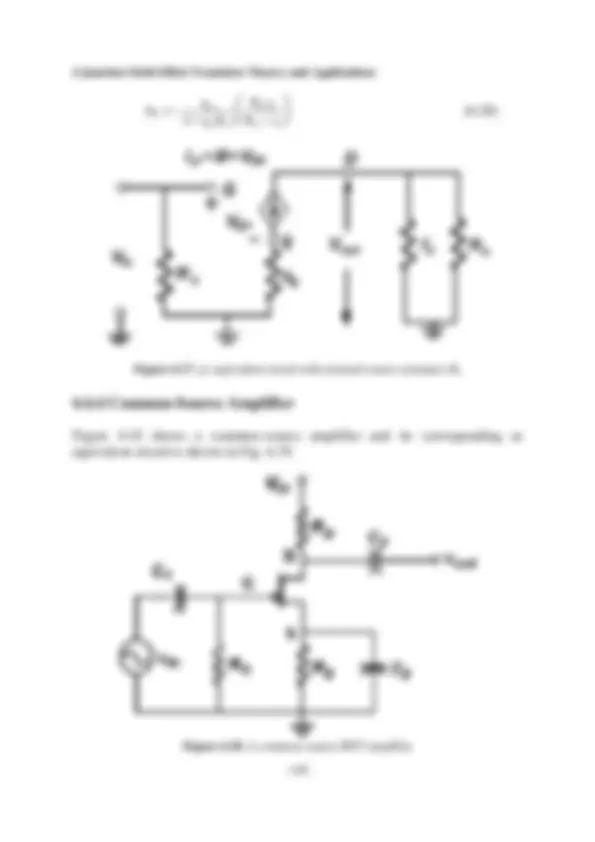

Figure 4.18 shows a common-source amplifier and its corresponding ac equivalent circuit is shown in Fig. 4.19.

Figure 4.18: A common source JFET amplifier